-

TSMC

TSMC has advised its clients to book foundry capacity well in advance for their 7nm chip demand for the entire 2020, according to industry sources.

7nm issues continue. Now TSMC owners artificially hold 7nm production as they are happy with profits and have no idea how to fix low yields.

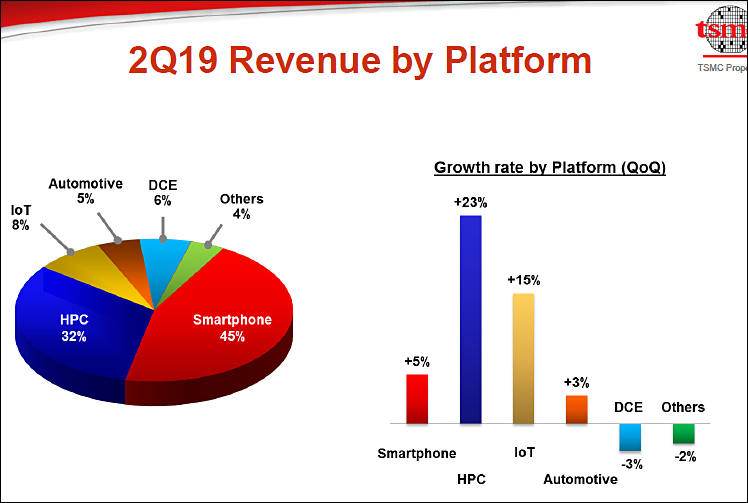

TSMC is expected to see its revenues in the second half of 2019 jump 32% from the first half - more than three times the 10% growth rate expected for the entire IC industry during the same period, IC Insights said. "There is little doubt that 7nm application processors for new smartphones from Apple and Huawei are driving the forecast for a strong second-half rebound in TSMC's sales".

Yes, TSMC and Apple with AMD are ripping you big part with 7nm.

TSMCis expected to have over 7x the dollar volume sales at sub-40nm processes as compared to the combined 2019 total of Globalfoundries, UMC, and SMIC (US$22.9 billion versus US$3.2 billion)

Here we have actual monopoly.

It took eight quarters for the foundry's 40-45nm technology to secure greater than 20% of its total sales, five quarters for its 28nm process to exceed that threshold, and only three quarters for its 7nm process to account for more than 20% of its quarterly revenue.

And it is growing fast.

-

Intel still has high hopes

GlobalFoundries laying off more than 400 workers at its Fab 8 computer chip factory in Malta last year may have benefited Intel. The staff were laid off after GloFlo decided not to bother with 7nm and to stick with the current cutting-edge 14-nanometre chips, GlobalFoundries was able to reduce its research and development expenses significantly.

Intel is building a $7 billion chip factory known as Fab 42 outside of Chandler, Arizona that is expected to make 7-nanometre chips eventually, and former GlobalFoundries workers that had been part of the 7-nanometre team at Fab 8 would be valuable to Intel as it gets its Fab 42 up and running.

According to LinkedIn dozens of former GlobalFoundries employees have found a home with Intel.

Best Intel hopes now are that to invest funds will want to keep two modern process manufacturers, despite any costs. Otherwise we can see slow Intel demise as 10nm process is clearly total failure for now.

-

The lead time for production of 7nm chips at Taiwan Semiconductor Manufacturing Company (TSMC) has extended to nearly six months from the previous two months because of strong demand, according to industry sources.

It is not much of demand issue, but issue of still quite low yields. Hence AMD design optimized for large number of defects.

-

Ryzen 7nm chips can have serious issues with reliability

The original limits for Ryzen 3000 SKUs were:

- 3600 = 4100MHz (80-95°C) / 4200MHz (< 80°C)

- 3600X = 4200MHz (80-95°C) / 4400MHz (< 80°C)

- 3700X = 4200MHz (80-95°C) / 4400MHz (< 80°C)

- 3800X = 4300MHz (80-95°C) / 4550MHz (< 80°C)

- 3900X = 4400MHz (80-95°C) / 4650MHz (< 80°C)

Since then, it appears that the HighTemperature limit has been reduced further to 75°C (from 80°C). New SMUs also have introduced "MiddleTemperature" limit, but that gets disabled when PBO is enabled.

AMD privately discovered fast degradation of CPU dies due to small 7nm process, such fats that it can break within warranty period.

Reliability of Sandy Bridge 32nm CPUs is around 10x-15x more compared to current 7nm process, and it still runs on same or higher clocks. Issue with new process is extreme leaks that can be up to 10x larger than on old processes.

-

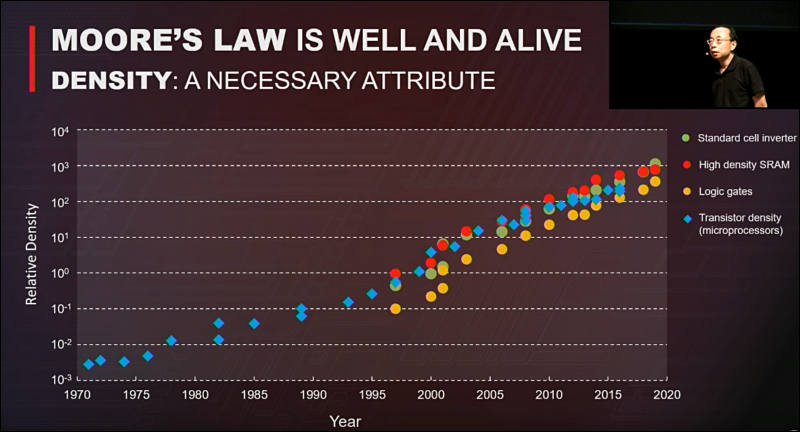

TSMC on Moore Law

First, let's discuss the elephant in the room. Some people believe that Moore's Law is dead because they believe it is no longer possible to continue to shrink the transistor any further. Just to give you an idea of the scale of the modern transistor, the typical gate is about 20 nanometers long. A water molecule is only 2.75 Angstrom or 0.275 nanometer in diameter! You can now start counting the number of atoms in a transistor. At this scale, many factors limit the fabrication of the transistor. The primary challenge is the control of materials at the atomic level. How do you place individual atoms to create a transistor? How do you do this for billions of transistors found on a modern chip? How do you build these chips that have billions of transistors in a cost effective manner?

To address this squarely, TSMC has recently announced our N5P node which further expands our leadership beyond the N5 node that will feature the world’s highest transistor density and offer the fastest performance. After being exposed to our technology roadmap, I can safely state that TSMC has many years of pioneering and innovation ahead of us where we will continue to shrink the individual transistor and continue to improve density. You will hear more from us in the coming months and years as we progress to new nodes.

Beyond the individual transistor, we also need to look at the system level density. Circling back and looking at the classic compute tasks of CPUs and GPUs, the modern chip has extremely fast transistor clock speeds that approach 5 gigahertz and beyond. The central challenge to these compute tasks is actually to keep the CPU and GPU cores fed with data. While this is classically a software challenge, modern architectures and methods for threading have squarely put the performance bottleneck at the hardware level. We have finally seen the limitations of memory caching in the era of big data analytics and AI.

To feed modern fast CPUs, GPUs and dedicated AI Processors, it is critical to provide memory that is both physically closer to the cores that are requesting the data for improved latency, in addition to supplying a higher bandwidth of data for the cores to process. This is what device level density provides. When memory is collocated closer to the logic cores, the system achieves lower latency, lower power consumption and higher overall performance.

Some of you may think that this is a system level concern and not an intrinsic attribute of a device technology. This may be strictly true in the past but the line is already getting blurry between the definition of a chip and the definition of a system. The line will continue to get more blurry and eventually will be completely eliminated. We have now transitioned from an era of design-technology co-optimization (DTCO) to system-technology co-optimization (STCO).

https://www.tsmc.com/english/newsEvents/blog_article_20190814.htm

-

Dreams about 3D stacking from company who lost the battle already

GLOBALFOUNDRIES, the world’s leading specialty foundry, today announced that it has taped-out an Arm®-based 3D high-density test chip that will enable a new level of system performance and power efficiency for computing applications such as AI/ML and high-end consumer mobile and wireless solutions. The new chip was fabricated using GF’s 12nm Leading-Performance (12LP) FinFET process and features Arm’s mesh interconnect technology in 3D that allows data to take a more direct path to other cores, minimizing latency while increasing data transfer rates as demanded by data centers, edge computing and high-end consumer applications.

The delivery of this chip demonstrates the fast progress that Arm and GF are making in researching and developing differentiated solutions that enable improvements in device density and performance for scalable high-performance computing. Moreover, the companies validated a 3D Design-for-Test (DFT) methodology, using GF’s hybrid wafer-to-wafer bonding that can enable up to 1 million 3D connections per mm2, extending the ability to scale 12nm designs long into the future.

“Arm’s interconnect technology in 3D enables the semiconductor industry to augment Moore’s Law to address a greater diversity of computing applications,” said Eric Hennenhoefer, vice president, Arm Research. “GF’s expertise in fabrication and advanced packaging capabilities, combined with Arm technology, gives our mutual partners additional differentiation to venture into new paradigms for next generation, high-performance computing.”

-

Ryzen 3xxx supply is really bad now

AMD is saved by preorders and promises, but real supply is quite low and can't keep up with orders.

AMD already postponed announcement 2 times, but due to quite low TSMC yields and due to fact that 7nm lines are fully loaded with Apple and Huawei chips, they can't do better.

Rumors are that up to 30% of AMD chips go to trash bin being fully functional as they can't keep the frequency standards, many works properly only up to 2-2.3Ghz.

-

On why CPUs are so heavily guarded

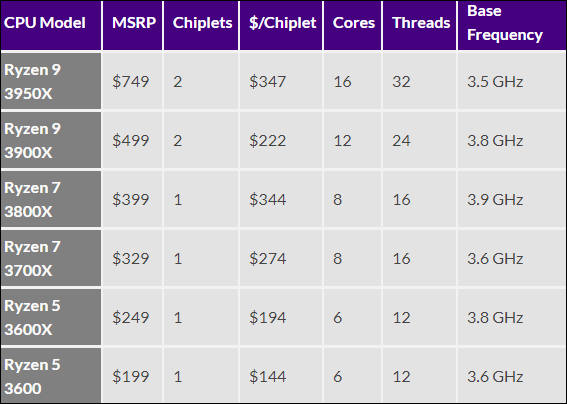

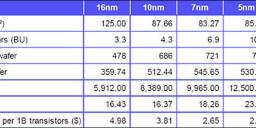

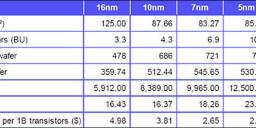

Note that 1st gen Ryzen costs make no sense here.

And here is per chiplet money that AMD gets:

sa9269.jpg799 x 135 - 28K

sa9269.jpg799 x 135 - 28K

sa9270.jpg567 x 404 - 38K

sa9270.jpg567 x 404 - 38K -

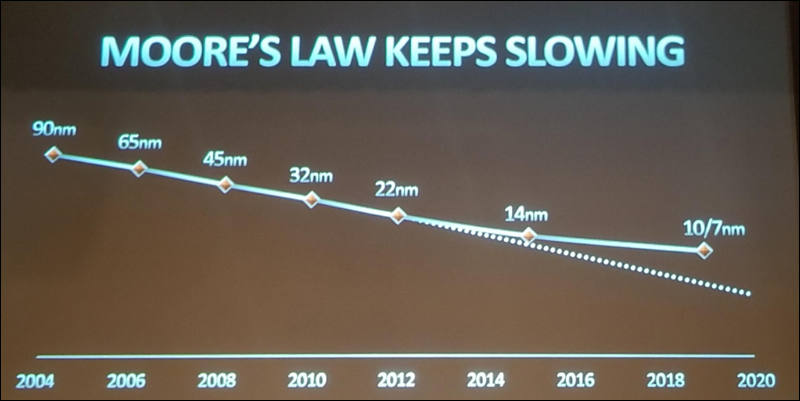

Moore’s Law has run out of gas, “and that is profound,” said Victor Peng, CEO of Xilinx.

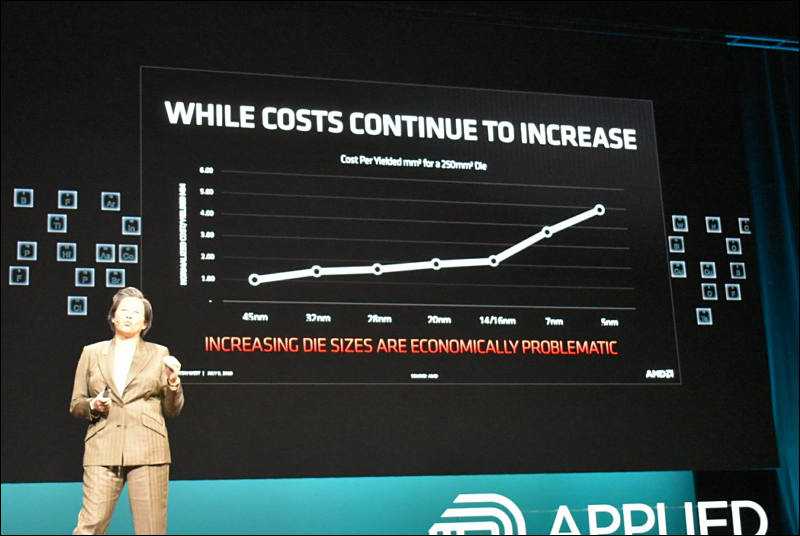

“You can get one of the three, it’s hard to get two of three, and I would challenge anyone who says they can get three of the three,” he said. Today’s extreme ultraviolet (EUV) lithography systems only remove the complexity of multi-patterning today’s chips, the 7-5-3-nm names of the latest nodes “are all marketing numbers, and no one has fixed the interconnect problem.”

“The cost of designing a 5-nm chip will be astronomical,” limiting the node’s use to a few companies who “can amortize it across multiple designs. Because of the constraints of Moore’s Law, you have to work harder — there’s no freebie in optical scaling anymore.”

-

AMD processors play more significant role in TSMC revenues

-

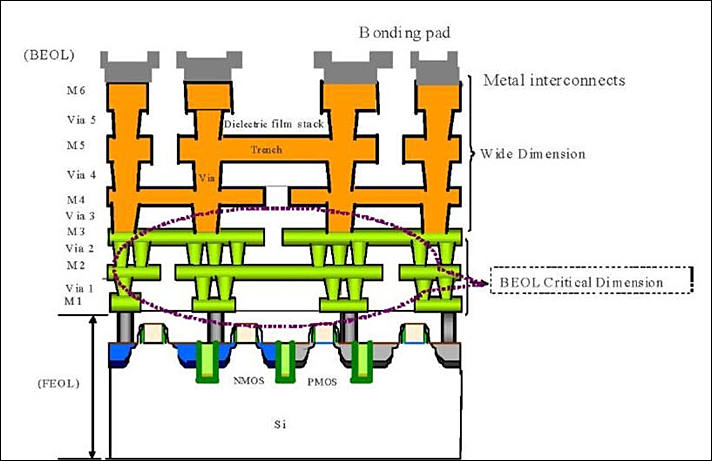

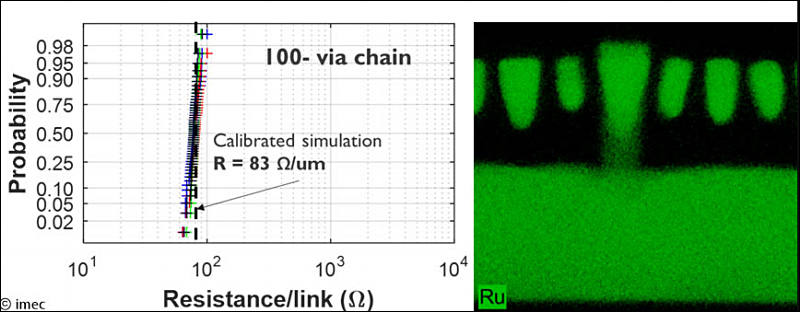

3nm marketing nanometers will be tough

This week, at its technology forum ITF USA 2019, imec, a world-leading research and innovation hub in nanoelectronics and digital technologies, presents a dual-damascene 21nm pitch test vehicle relevant for manufacturing the 3nm logic technology node. With this test vehicle, a 30 percent improvement in resistance-capacitance product (RC) was obtained compared to previous generations, without impacting reliability. The need for implementing scaling boosters such as self-aligned vias and self-aligned blocks in 3nm and beyond interconnect technologies has been demonstrated.

-

Watch how capitalism criminals work

Wafer processing equipment sales will fall 19.1% in 2019 to US$42.2 billion. The other front-end segment, consisting of fab facilities equipment, wafer manufacturing, and mask/reticle equipment, is expected to slide 4.2% to US$2.6 billion this year. The assembly and packaging equipment segment is on track to decline 22.6% to US$3.1 billion in 2019, while semiconductor test equipment is forecast to decrease 16.4% to US$4.7 billion this year.

Most of this issues are due to DRAM and NAND manufacturers trying to return to huge 300-600% margins by cutting output.

-

How it looks in smartphone space

With rising heat dissipation demand from major vendors including Samsung Electronics, LG Electronics, Huawei, Oppo and Xiaomi for their 5G smartphones, half of cooling module shipments for smartphones in the second half of 2019 will be vapor chamber-based solutions, and the other half heatpipe-based ones, according to industry sources.

And it is only small beginning.

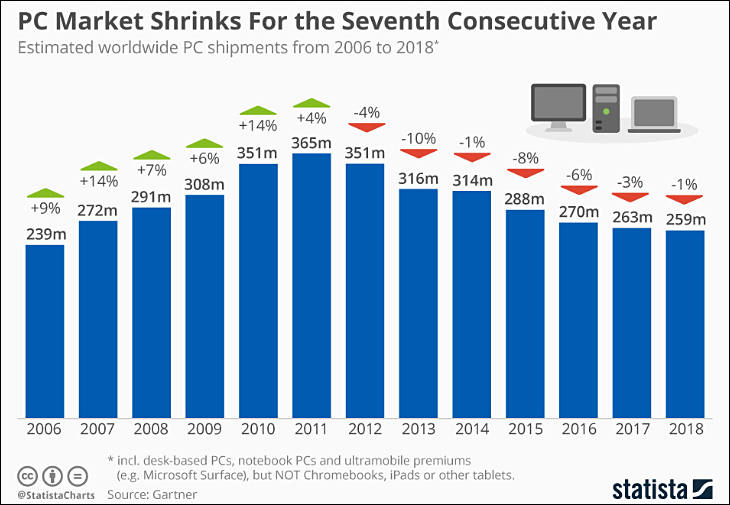

Fall of smartphone huge market will be unprecedented and it will destroy some of leading semiconductors manufacturers.

-

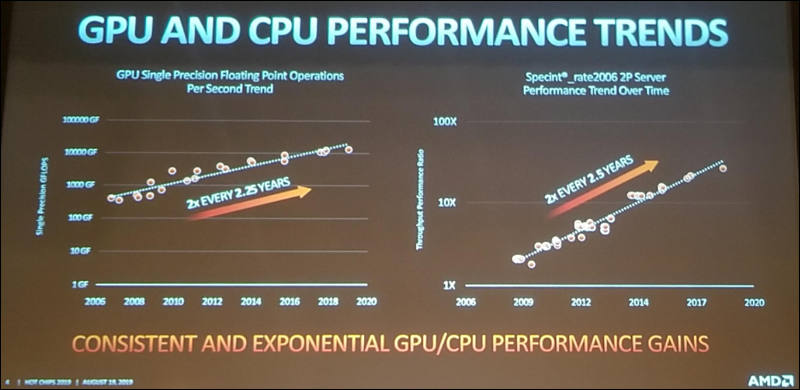

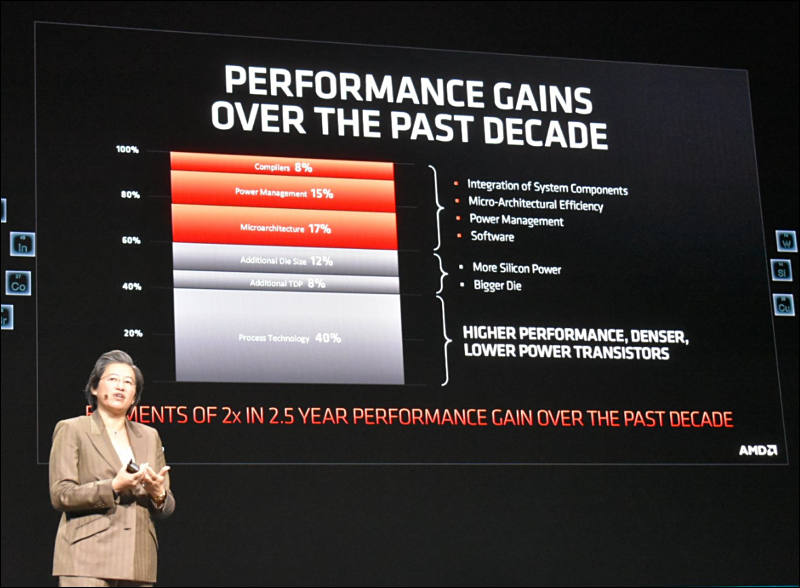

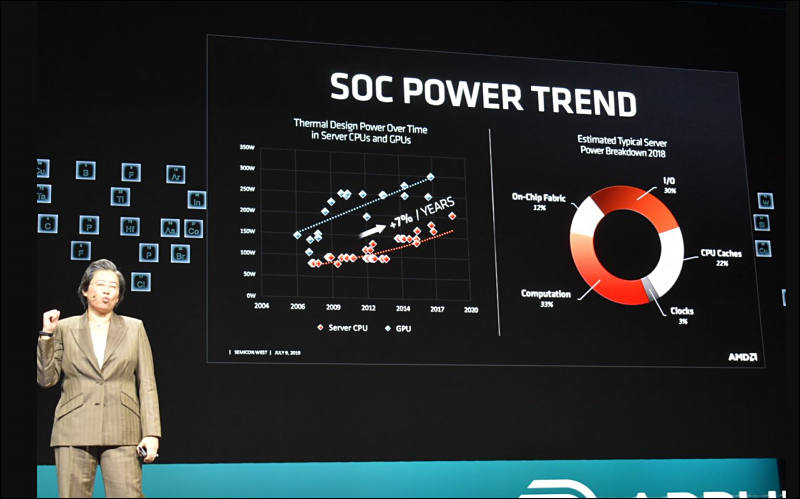

Interesting slides

-

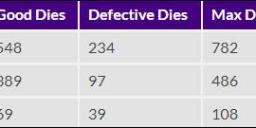

Some chips cost estimation table

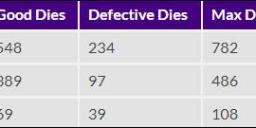

Btw, TSMC 7nm yields for not too large chips like AMD Zen 2 reached 80-85% now.

For previous process on same stage it had been around 90-95%.

sa9102.jpg734 x 249 - 53K

sa9102.jpg734 x 249 - 53K -

“It's going to keep going,” said Jim Keller, a semiconductor rock star who joined Intel last year as senior vice president of silicon engineering, and a cohost of the event. “Moore’s law is relentless”

“The working title for this talk was ‘Moore’s law is not dead but if you think so you’re stupid,’" he said Sunday. He asserted that Intel can keep it going and supply tech companies ever more computing power. His argument rests in part on redefining Moore’s law. “I’m not pedantic about Moore’s law talking just about transistors shrinking—I’m interested in the technology trends and the physics and metaphysics around that,” Keller says. “Moore’s law is a collective delusion shared by millions of people.”

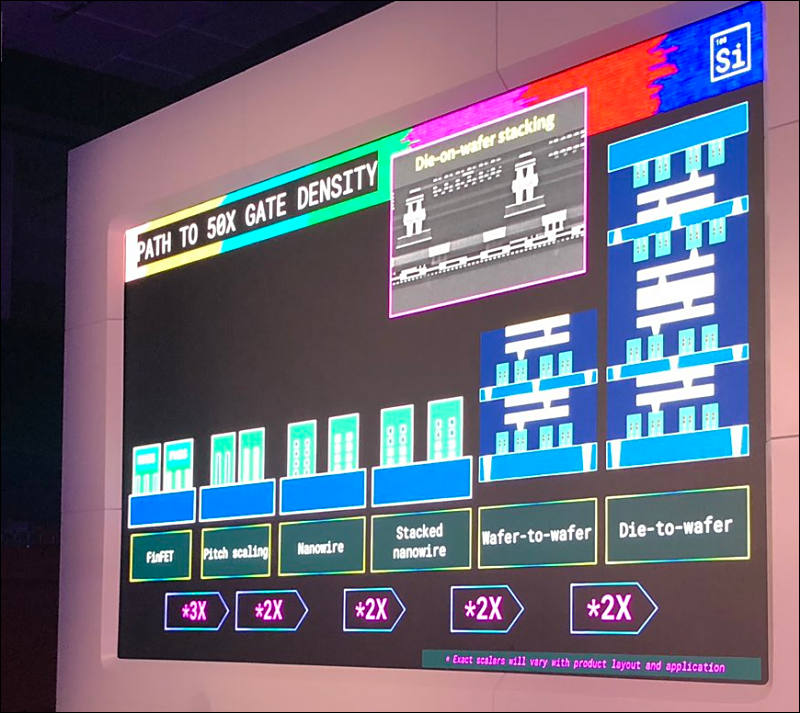

Keller said Sunday that Intel can sustain that delusion, but that smaller transistors will be just one part of how. On the conventional side, he highlighted Intel’s work on extreme ultraviolet lithography, which can etch smaller features into chips, and smaller transistor designs based on nano-scale wires due to arrive in the 2020s.

Keller also said that Intel would need to try other tactics, such as building vertically, layering transistors or chips on top of each other. He claimed this approach will keep power consumption down by shortening the distance between different parts of a chip. Keller said that using nanowires and stacking his team had mapped a path to packing transistors 50 times more densely than possible with Intel's 10 nanometer generation of technology. “That’s basically already working,” he said.

All this vertical 3D stuff does not work for heavy load chips like CPUs. Only for their SRAM and IO parts may be.

-

Same as 2011 had been year of 2500K, 2019 is the year of Ryzen 3xxx, and will be next peak before even faster reduction. Industry won't be able to scale further from 16 cores without drastic price increases and thermal output increase.

-

Samsung can start making 14nm chips, including CPUs for Intel

Intel stopped any further investment in failed 10nm process.

Korean Sedaily leaked that from Q4 of 2019 Samsung will start making 14nm products for Intel. Most probably it'll be only first deal part, as Intel for now do not have any working advanced processes, with 10nm lines being able to make only 10nm 2 core chips with huge failure rates (up to 95%).

7m, and further 5nm processes could be necessary for Intel to survive, and such way we will be down to only two companies who will continue to making any progress in semiconductors manufacturing.

Howdy, Stranger!

It looks like you're new here. If you want to get involved, click one of these buttons!

Categories

- Topics List23,993

- Blog5,725

- General and News1,354

- Hacks and Patches1,153

- ↳ Top Settings33

- ↳ Beginners256

- ↳ Archives402

- ↳ Hacks News and Development56

- Cameras2,368

- ↳ Panasonic995

- ↳ Canon118

- ↳ Sony156

- ↳ Nikon96

- ↳ Pentax and Samsung70

- ↳ Olympus and Fujifilm102

- ↳ Compacts and Camcorders300

- ↳ Smartphones for video97

- ↳ Pro Video Cameras191

- ↳ BlackMagic and other raw cameras116

- Skill1,960

- ↳ Business and distribution66

- ↳ Preparation, scripts and legal38

- ↳ Art149

- ↳ Import, Convert, Exporting291

- ↳ Editors191

- ↳ Effects and stunts115

- ↳ Color grading197

- ↳ Sound and Music280

- ↳ Lighting96

- ↳ Software and storage tips266

- Gear5,420

- ↳ Filters, Adapters, Matte boxes344

- ↳ Lenses1,582

- ↳ Follow focus and gears93

- ↳ Sound499

- ↳ Lighting gear314

- ↳ Camera movement230

- ↳ Gimbals and copters302

- ↳ Rigs and related stuff273

- ↳ Power solutions83

- ↳ Monitors and viewfinders340

- ↳ Tripods and fluid heads139

- ↳ Storage286

- ↳ Computers and studio gear560

- ↳ VR and 3D248

- Showcase1,859

- Marketplace2,834

- Offtopic1,320