It allows to keep PV going, with more focus towards AI, but keeping be one of the few truly independent places.

-

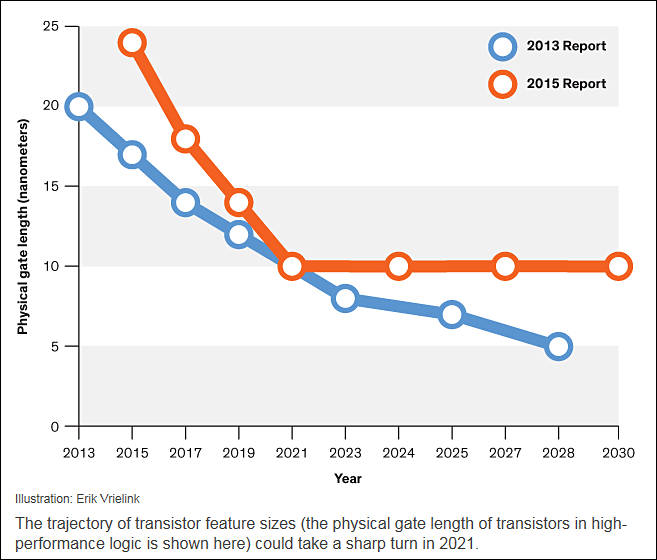

After more than 50 years of miniaturization, the transistor could stop shrinking in just five years, this is the prediction of the 2015 International Technology Roadmap for Semiconductors, which was officially released earlier this month.

After 2021 it will no longer be economically desirable for companies to continue to shrink the dimensions of transistors in microprocessors. Instead, chip manufacturers will turn to other means of boosting density, namely turning the transistor from a horizontal to a vertical geometry and building multiple layers of circuitry, one on top of another.

19 companies were developing and manufacturing logic chips with leading-edge transistors in 2001. Today, there are just four: Intel, TSMC, Samsung, and GlobalFoundries.

This guys did not tell you full truth. For all last manufacturer processes companies had marketing process values and real process values. In old good times each generation of process really meant proportional reduction of all elements, it is no longer the case. Especially with 14nm processes that are not really 14nm.

Optimistic statements with many 3D wafers and such are overly optimistic. Due to difficulties such process is very costly and available to top manufacturers only. All such processes are not usable in high speed and thermally intense areas due to cooling issues, this mean GPUs and CPUs. Now it is only some flash memory that is made using similar approach.

img961.jpg657 x 560 - 51K

img961.jpg657 x 560 - 51K -

The Taiwanese company remains the largest contract chip maker in the world, its ability to rhythmically master advanced lithographic standards and offer chip production on them in the quantities needed is attracting many customers.

By some estimates, it will charge twice as much per silicon wafer with 2nm chips as it would for 4nm or 5nm chips.

At least, such calculations are cited by the Commercial Times, emphasizing at the same time that the new lithography steps noticeably increase the costs of manufacturers, and therefore price increases are inevitable. In particular, if at the development of 16nm technology was enough $100 million in research and development costs, in the case of 3nm technology, this amount is already at risk of not being within the range of $4 to $5 billion. Moreover, for this class of processes usually requires a new enterprise with advanced equipment, which costs from $15 to $20 billion. All this leads to the fact that a silicon wafer with 2nm chips can cost the customer $ 30,000 at least. Especially since TSMC itself will have to pay more for the same energy resources due to the concentration of its advanced facilities in Taiwan.

-

EU countries and the region's parliament are about to approve a plan that will help the European semiconductor industry catch up with Asia and the US, Reuters reported. The implementation of the plan, known as the "Chip Act" by analogy with the same American law, will cost the EU 43 billion euros.

The European "Chip Law" was announced last year when EU countries decided to reduce their dependence on US and Asian semiconductor manufacturers. This was prompted by the pandemic-induced shortage of chips, which in 2020-2021. caused significant damage to a number of European enterprises, and primarily to automakers.

Present issues can be solved only with free (read - newly printer by goverment) money.

-

On equipment criminal cartel

ASML Holding NV, supplier of lithography technology to the semiconductor industry. This is the only company capable of producing unique devices worth about 160 million euros. Even though high-tech stocks have fallen, ASML stock is now worth ten times what it was eight years ago.

In addition to ASML, there are two other semiconductor equipment companies in the Netherlands. These are BE Semiconductor Industries NV (20x growth in 10 years) and ASM International NV (10x growth in 10 years), which controls more than half of the world market for atomic layer deposition equipment. Since few companies can manufacture such sophisticated equipment, they can set prices at their discretion without fear of losing business to competitors.

-

To quote wikipedia, "Quantum computing is a type of computation whose operations can harness the phenomena of quantum mechanics, such as superposition, interference, and entanglement."

-

Dude are you sure you know what you are talking about ?

Seems you are confused please elaborate on your idea .

-

Quantum Computers take blueprints of idea's and things and then make them using Quantum Physics like a 3D printer would make a piece of plastic.

Their applications are in Health, Technology and Manufacturing.

They are not as popular as a Laptop or iphone.

-

Quantum computers are in the 1950s if we talk about development they are not perfected.

When we have normal temperature, optical quantum computers in small size, I think we can call that developed quantum computing, shits not even perfected.

-

Quantum Computers also need budget money injected into

-

Quantum Computers have already been perfected and will be operational in the future.

-

Alleged time travelers.

That’s really way out of topic but interesting to hear what you have to say about that.

Artificial Consciousness can only be achieved by quantic computing.

-

@Vitaliy_Kiselev I agree.

What are we hacking though?

There's many ways to create Conciousness, as all types of matter have it because they are made from the same source particles.

I've heard alleged Time-Travellers say that Computers will eventually replace the Justice system and run Cities because of the historical corruption that has occurred in those "Industries".

-

And you've all heard many times Moore's Law is slowing down. Moore's Law is dead. What does that mean? It's not that there's not going to be exciting new transistor technologies.

Actually, I can see exciting new transistor technology for the next -- as far as you can really plot these things out, is about six to eight years, and it's very, very clear to me the advances that we're going to make to keep improving the transistor technology, but they're more expensive. It used to be the old Moore's Law, right?

You could double the density in every 18 to 24 months, but you'd stay at that same cost band. Well, that's not the case anymore. So, we're going to have innovations in transistor technology. We're going to have more density. We're going to have lower power, but it's going to cost more. So, how you put solutions together has to change.

And we did see that coming, and that was part of the motivation of the Infinity architecture that we just spoke about because it allowed us to be very modular and how that we design each of the elements and that put us in a position to be able to leverage chiplets. Chiplets is really a way to just rethink about how the semiconductor industry is going forward.

There's a lot of innovation yet to go because it's going to be the new point of how solutions to put together. It used to be a motherboard and you put all these discrete elements in the motherboard. What will keep innovation going and we'll keep, I'll say, a Moore's Law equivalent, meaning that you continue to really double that capability every 18 to 24 months is the innovation around how the solution is put together.

It will be heterogeneous. It won't be homogeneous. So you're going to have to use accelerators, GPU acceleration, specialized function, adaptive compute like we acquired with Xilinx, which closed in February this year. So those elements are going to have to come together and then how you integrate it is you're going to see tremendous innovation on how those come together and it really will keep us on pace, and we actually have to because you can just look at the demands of computing, they haven't slowed down one iota. In fact, they're escalating rapidly with AI becoming more and more prevalent.

-

By the end of the year, a research center will open in Japan as part of a partnership project with the United States, on the basis of which the development of technologies for mass production of chips using the 2 nm process technology will be carried out. In the future, the joint project will help companies build stable supply chains and insure against tensions around the industry leader, Taiwan.

The center will be created on the basis of a new research institute, which will also open this year - as part of the project, it is planned to use equipment and involve specialists from the US National Center for Semiconductor Technology. Initially, researchers from the two countries will focus on advanced chips based on the 2nm process technology, which will improve performance and reduce energy consumption compared to existing solutions. The center will also set up a prototype production line, and the ultimate goal of the project is to start mass production of the chips in Japan by 2025.

And again - it will be direct budget money injected into business.

-

U.S. Secretary of Commerce Gina Raimondo said on Wednesday that lawmakers appear to be moving to carve off $52 billion in semiconductor chips manufacturing subsidies from a larger bill on boosting U.S. competitiveness with China.

"Things seem to be coalescing around the path of chips, or maybe chips plus a thing or two, and getting it done this month," Raimondo told Reuters in a telephone interview. "It seems like that's what Congress is coalescing around."

A smaller bill could also include investment tax credits for semiconductor manufacturing, she said, but emphasized that discussions are very fluid. "That is a good outcome because the worst outcome is getting nothing done by Aug. 4," when Congress leaves for summer recess, she said. "Better to get chips plus a little done than nothing done."

Another round of free money to this guys.

-

The CEO of GlobalFoundries, the world's fourth-largest contract chipmaker, is fond of repeating that by the end of the decade, the semiconductor market will double to a trillion US dollars. He is also convinced that in order to overcome the shortage of components, a comparable amount must be invested in their production.

Topical considerations Tom Caulfield (Tom Caulfield), according to Seeking Alpha, this week shared with the audience of the TV channel CNBC. The global expansion of semiconductor production, according to the head of GlobalFoundries, will continue without regard to possible macroeconomic difficulties such as the “bottlenecks” currently observed in the supply chains of components. All problems will be solved sooner or later, according to Caulfield, and chip production will continue to grow.

By 2024, the company will increase its own production capacity by 60% compared to 2020 levels. Already, GlobalFoundries has orders for two years in advance; it is not afraid of a possible decrease in demand in certain market segments. Firstly, demand is now falling in the segment of PCs and budget smartphones, and it is weakly dependent on them. Second, any modest gaps in demand in one direction can be offset by others, since global demand still exceeds supply by 20%.

-

Samsung plans to increase the price of its chip manufacturing services by 15% to 20% in the second half of 2022. At the same time, the production of products based on mature technical processes will become more expensive. The company has already agreed with some of its clients, while negotiations are still ongoing with the rest, Bloomberg reports, citing sources close to the issue. Samsung itself declined to comment.

Nice, more inflation.

-

The European Union (EU) has published a set of provisions in the EU Chip Act, which is intended to be "Europe's blueprint for regaining world leadership in the semiconductor industry," according to PCGamer. Europe wants to join the semiconductor technology race and bring the results of its advanced research to production, as the IMEC research center is already engraving 1.4 nm wafers. By 2030, it is planned to invest 11 billion euros in the creation of a comprehensive platform for the industrial implementation of advanced technological processes through the joint efforts of the EU member states.

-

American chip maker Texas Instruments announced plans to invest $3.5 billion annually in the production of semiconductor chips in the United States until 2025 as part of the fight against the current deficit in electronic components. This is significantly more than the capital investments that the company has made in recent years.

Of course, current profits are staggering.

-

As I said before - people will pay now to greedy basters from their taxes

Not having managed to do this before the end of last year, members of the US Congress this week nevertheless voted for the adoption of a package of legislative measures to stimulate the development of the domestic semiconductor industry. The House of Representatives voted to pass the bill, which includes $52 billion in subsidies. About $39 billion will go directly to building new semiconductor manufacturing facilities.

Ripping has no limits lately.

-

Its a treason then

A shortage in the supply of semiconductors has led to an increase in the cost of purchasing chips among original equipment manufacturers (OEMs). They had to spend 25.2% more than a year earlier. It follows from the report of analytical agency Gartner.

Gartner's list of the top 10 semiconductor spenders in 2021 is topped by Apple and Samsung. The former accounted for nearly 12 percent of global chip purchases in 2021. The company spent $68.269 billion on the purchase of chips. The South Korean giant spent $45.775 billion on the purchase of chips. In percentage terms, Samsung increased its chip spending by 28.5% compared to 2020.

-

Capitalism as case of shortages

Semiconductor shortage problems will persist until at least mid-2022, as industry players try to stock up to normal levels but do not invest in mature technology, research firm IDC said.

The company believes that one of the reasons for this situation is too little investment in non-advanced technological processes - they are necessary in the production of vital components for the automotive industry and other market segments. According to IDC, the market for semiconductor products is still in short supply of products that are produced on "obsolete" equipment. We are talking about technical processes of 40 nm or more - they are involved, for example, in automotive electronics, LCD controllers and power management.

Last year, up to 67% of semiconductor products were manufactured using such technologies, rather than advanced solutions at 16 nm or less. Products based on the most advanced technologies account for only 15% of wafer shipments, but they generate 44% of total revenue. In this regard, advanced productions receive more significant investments in comparison with mature solutions.

This guys aim for profit, not real needs.

-

TSMC invests roughly 50% of its revenue in equipment compared to Samsung's 70%. Samsung announced it will begin mass production using its 3nm process in the first half of 2022, overtaking TSMC. However, even if they are unable to overtake TSMC's market share in the short term, taking the initiative to announce mass production using the 3nm process is a strategic move. The announcement proves Samsung is working diligently to reach its goal of becoming the world's number one system semiconductor maker by 2030.

-

The development of new technologies will require new personnel, and someone has to work at newly created enterprises. TSMC's engineering staff will increase by 8,000 this year, MediaTek is going to hire 2,000 engineers.

This is reported by the Japanese edition of the Nikkei Asian Review, citing informed sources. Last year, TSMC hired about 8,000 people, so this year's hiring plans will ensure that the pace of staff growth continues. Now TSMC has about 60,000 employees worldwide, although the bulk of the workforce is concentrated in Taiwan.

In the case of MediaTek, which develops mobile processors, the engineering staff is expected to increase by 2,000 this year. In the past, the company has hired about the same number, and in total, 19,300 people work for the benefit of MediaTek. In addition to staff in Taiwan, this developer will attract talent from within India. About 1,000 specialists in the field of research and development are already working here.

-

This year, TSMC intends to increase capital expenditures by at least a third of last year's level, to $40-44 billion. Management forecasts that TSMC will increase revenue by 15-20% annually in the coming years, while the profit margin will rise to at least 53% . The need to spend more will not undermine the profitability of the business.

Howdy, Stranger!

It looks like you're new here. If you want to get involved, click one of these buttons!

Categories

- Topics List23,991

- Blog5,725

- General and News1,353

- Hacks and Patches1,153

- ↳ Top Settings33

- ↳ Beginners256

- ↳ Archives402

- ↳ Hacks News and Development56

- Cameras2,367

- ↳ Panasonic995

- ↳ Canon118

- ↳ Sony156

- ↳ Nikon96

- ↳ Pentax and Samsung70

- ↳ Olympus and Fujifilm101

- ↳ Compacts and Camcorders300

- ↳ Smartphones for video97

- ↳ Pro Video Cameras191

- ↳ BlackMagic and other raw cameras116

- Skill1,960

- ↳ Business and distribution66

- ↳ Preparation, scripts and legal38

- ↳ Art149

- ↳ Import, Convert, Exporting291

- ↳ Editors191

- ↳ Effects and stunts115

- ↳ Color grading197

- ↳ Sound and Music280

- ↳ Lighting96

- ↳ Software and storage tips266

- Gear5,420

- ↳ Filters, Adapters, Matte boxes344

- ↳ Lenses1,582

- ↳ Follow focus and gears93

- ↳ Sound499

- ↳ Lighting gear314

- ↳ Camera movement230

- ↳ Gimbals and copters302

- ↳ Rigs and related stuff273

- ↳ Power solutions83

- ↳ Monitors and viewfinders340

- ↳ Tripods and fluid heads139

- ↳ Storage286

- ↳ Computers and studio gear560

- ↳ VR and 3D248

- Showcase1,859

- Marketplace2,834

- Offtopic1,320